介绍

Custom IP Core factory 是一款在线工具,可用于即时定义、生成和下载 IP cores的自定义配置。用户几乎可以定义任意数量的数据流(streams),这些数据流的属性能够最大程度地满足特定应用的需求。

下载完成后, custom IP core bundle 中的文件会部分替换演示包(demo bundle)或特定 FPGA 系列示例设计中的文件。因此,建议先完成演示包的实现流程,然后再应用自定义的 IP core。请注意, Xillyp2p没有对应的演示包,只有一个示例设计。

强烈建议在尝试集成 custom IP core之前,先充分理解演示包或示例设计的工作原理。只需简要学习示例设计中提供的 'xillydemo' 模块或 Verilog/VHDL 代码示例,即可避免许多常见错误。

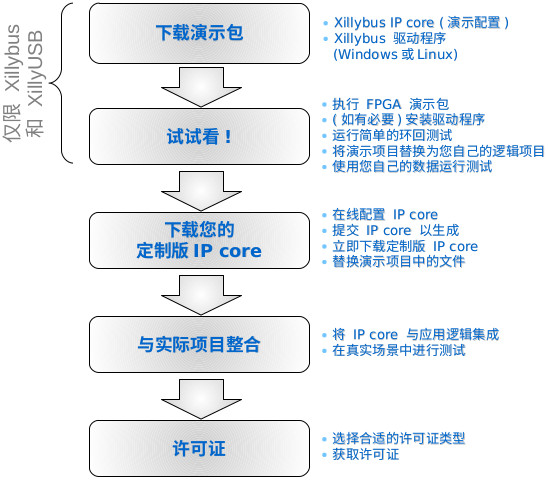

建议的工作流程如右图所示。

使用 IP Core Factory

建议您使用有效的电子邮件地址(例如 QQ 或类似服务)进行注册。这样可以确保配置信息被保存。此外,生成和下载自定义 IP cores也必须注册。

- 首次进入 Factory时,输入所需 IP core 的基本定义(例如设置 FPGA 系列、操作系统,并选择是否像演示包那样从设备文件(device files)开始)。

- 适用于 Xillybus 和 XillyUSB: 根据需要添加新的设备文件,或移除现有的设备文件。对于每个新的设备文件,请设置其方向、应用类型、数据宽度和预期带宽。建议至少在第一阶段启用“Autoset internals”选项。此外,请务必准确设置参数(而不是试图通过夸大带宽预期等方式来最大化性能)。否则,可能会导致整体性能欠佳。

- 对于 Xillyp2p: 在 FPGA和应用数据流之间建立所需的连接: 它们的方向、数据宽度、预期带宽以及是否应应用硬件流控制(flow control)。

- IP core设置完成后,点击网页上“generate core”链接提交配置信息。

- 等待 IP core 生成完成。这通常需要几分钟时间。密切关注 IP core的“status”属性。

- 下载自定义的 IP core ,并按照“readme”文件中的说明进行操作。

- 如果提交后需要更改配置,请使用“replicate”链接复制 IP core的配置。更改应在副本上进行。更改完成后,提交此配置以获取更新版本。

大胆试试吧

点击这里进入 IP Core Factory。