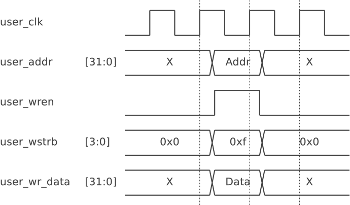

Write access waveform

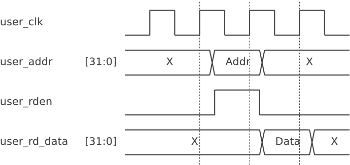

Read access waveform

Xillybus Lite is a simple kit (IP core + driver) for easy access of registers in the logic fabric (PL) by a user space program running under Linux on Xilinx Zynq-7000 EPP. Read and write operations take place as in a bare-metal program, with plain assignments involving a pointer to the registers.

Writing to a register is simply (in C)

volatile unsigned int *ptr = ... ; *ptr = value;

And reading from a register is

volatile unsigned int *ptr = ...; value = *ptr;

The pointer is initialized with a simple procedure, which can be copied from a demo program. Each use of this pointer induces an access cycle on the bus (memory caching is disabled on the allocated memory region) with an access rate of ~ 7M/sec. Xillybus Lite is hence no substitute for DMA-driven data transport.

The IP core handles the interface with the processor's AXI Lite bus, and presents a trivial local bus interface to the application logic. User interface waveforms are shown to the right.

There is also an interface for a hardware interrupt, allowing a Linux process to sleep until the interrupt signal is triggered.

Resources

- Xillybus Lite is deployed for immediate use on Xillinux (versions 1.1 and up).

- For inclusion in a non-Xillinux project for Zynq-7000, download the kit's bundle.

- Refer to the list of documents or download The Guide to Xillybus Lite.

Licensing

The Xillybus Lite IP core is released for any use at no cost. In particular, it may be downloaded, copied and included in binaries used and sold for commercial purposes with no limitation and without any additional consent nor specific licensing.

The Xillybus Lite driver for Linux is released under GPLv2, which makes it free for distribution under the same terms as the Linux kernel itself.