Introduction

Released in November 2020, the XillyUSB IP core is the Xillybus variant for USB 3.0 (SuperSpeed). Based upon direct usage of an FPGA’s MGT transceiver, this IP core implements a complete SuperSpeed USB device with a speed limit of 400 MBytes/s. With an adapter kit available for purchase (at about 75 EUR + shipping, see below), several popular FPGA development boards can be used to try out the XillyUSB IP core.

XillyUSB can of course be used on a custom board, by connecting four wires from the USB port connector to the FPGA along with a few passive components.

The primary use of XillyUSB is creating a high-speed data link between an FPGA and a laptop computer.

If you’re not familiar with Xillybus’ IP core for PCIe, it’s a good idea to make yourself acquainted with it first, as the XillyUSB IP core is merely a compatible version of the former, ported to the USB 3.0 (SuperSpeed) interface. The simple API on both FPGA and host side is retained: Just standard FIFOs on the FPGA and plain pipe-like device file I/O on the host side. As with other Xillybus variants, a dedicated Windows or Linux driver detects the FPGA, which behaves as an USB 3.0 device. Likewise, the IP Core Factory allows generating custom XillyUSB IP cores.

Another good reason to look at the PCIe variant is that it’s inherently better than its XillyUSB counterpart, not only because the former IP core has been around since 2011, but also because the PCIe bus allows the IP core more control on the data flow, and is generally more reliable: A PCIe device is essentially part of the host’s hardware, with short and carefully designed physical connections. USB, on the other hand, is intended for external, often temporary devices, which connect to the host through cables of varying quality. The fundamental expectation for reliability is different between these two interfaces.

XillyUSB is hence the preferred choice for applications that require a hotpluggable and external connection to the host, in particular laptop PCs.

As XillyUSB is based upon an FPGA’s MGT transceiver only (without a companion chip), it doesn’t support fallback into USB 2.0 or lower. It hence works only with USB 3.0 ports.

The list of supported FPGA boards can be found on XillyUSB’s download page.

Things to be aware of

USB 3.x is currently in a relatively early stage of wide adoption. Awareness of certain issues is required in order to ensure stable and reliable communication.

- Even though the physical link is normally error-free, low-quality equipment may cause bit errors on the wire. The XillyUSB IP core exposes diagnostic information which is useful for assessing the health of the physical connection.

- The host’s USB controller matters. Some are great, some aren't all that great, and all of them have a crucial influence on the performance of the USB data link. Some controllers are supported dramatically better on Windows compared with Linux. The maximal data rate also differs, as shown on this page for a handful of controllers.

- If you’re used to Xillybus for PCIe / AXI, there are several differences. In particular, the number of host-to-FPGA streams is limited, and using them simultaneously may cause latency issues.

- On some development boards, there are about 20 seconds from the configuration of the FPGA and the appearance of the USB device. This is normal, and discussed briefly on this page.

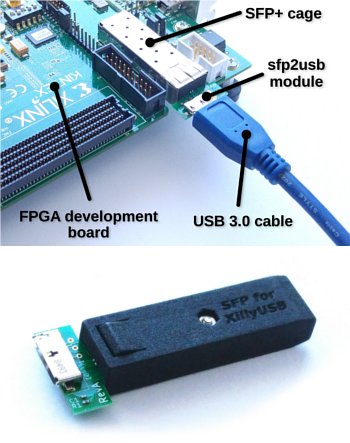

The sfp2usb adapter kit

As virtually no FPGA development board provides a USB 3.0 port, an adapter kit (shown in image above) is available for connecting the wires from an FPGA's MGT transceiver to a Micro-B SuperSpeed receptacle. The board’s SFP+ cage and connector are used for this purpose. This connector is often present on FPGA boards for use with an optical transceiver, exposing one of the FPGA’s MGT transceivers for the optical link.

Except for its mechanical enclosure, the adapter consists only of a PCB with the receptacle, capacitors, resistors and ESD protection components, and is plugged into the SFP+ instead of an optical transceiver. The SuperSpeed pins on the Micro-B USB receptacle are hence connected directly to the FPGA, with AC coupling as required per spec.

There is more information on the sfp2usb module on a separate page.

The adapter kit is available at this internet shop. It also includes a 1 meter long USB 3.0 cable, which connects to the standard Type-A port found on computer motherboards.